Binaarloogika funktsioonid

Funktsionaalset üksust, milles teostatakse binaarloogika põhioperatsioone, (näit. Boole loogikatehteid) nimetatakse loogikablokiks või ka lüliks. Graafiliselt kujutatakse lüli ristkülikuna, millel on sisendid ja väljundid. Binaarloogika põhioperatsioonide teostust saab kirjeldada ka erinevat tüüpi kontaktide abil.

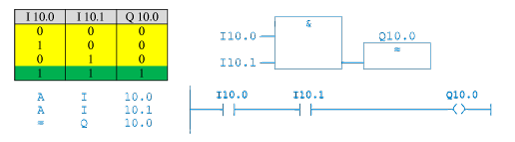

NING- ja VÕI-lülid

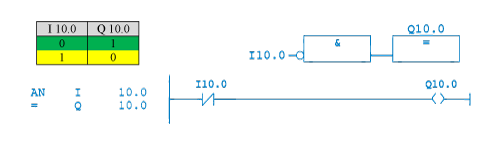

Binaarloogika NING-lüli (tehte) väljundis on signaal väärtusega 1, kui selle kõikides sisendites on signaal väärtusega 1. Väljundsignaal on 0, isegi kui ainult ühes sisendis on signaal 0. Joonisel 4.1 on kujutatud binaarloogika NING-lülid LAD, FBD ja STL keeles. NING-lüli võib omada rohkem kui kaht sisendit.

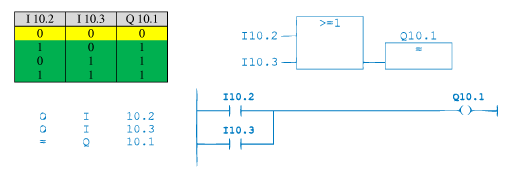

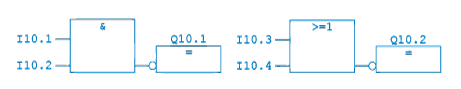

Binaarloogika VÕI-lüli (tehte) väljundis on signaal väärtusega 1, kui vähemalt ühes VÕI-lüli sisendis on signaal 1. Väljundsignaal on 0, kui kõikides sisendites on signaal 0. Joonisel 4.2 on kujutatud binaarloogika VÕI-lüli LAD, FBD ja STL keeles. VÕI-lüli võib omada rohkem kui kaht sisendit.

Tarkvara STEP 7 abil salvestatakse NING- ja VÕI-tehte tulemused PLC loogikaoperatsiooni tulemuse RLO bitti (RLO - result of logic operation). RLO biti väärtus ehk olek võib olla 1 või 0 [6]. NING- või VÕI-tehte algfaasis küsitakse esimese operandi signaali väärtust ja see salvestatakse kohe RLO bitti. NING- või VÕI-tehte teostamise järgmises faasis küsitakse ka teise operandi signaali väärtust, mis seejärel seotakse RLO bitti salvestatud väärtusega järgides binaaralgebra reegleid. Vahetulemus salvestatakse RLO bitti jne. Tehte teostamise lõpus salvestatakse RLO biti väärtus väljundlüli operandi(desse) või siis toimub programmis tingimuslik hüpe. Mõnikord on vaja (jõuga) muuta väljundlüli RLO biti väärtust 0 või 1 ilma mingi eelneva operatsioonita. Selleks saab kasutada STEP 7 STL keeles käske CLR ja SET.

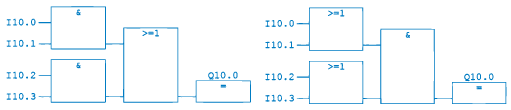

NING- ja VÕI-lülidest saab koostada keerukamaid loogikatehteid nagu NING-VÕI- ja VÕI-NING-loogikaühendused [16]. NING-VÕI-loogikaühenduses on NING-tehte väljund ühendatud VÕI-tehte sisendiga. VÕI-NING-loogikaühenduse puhul on vastupidi. Joonisel 4.3 on kujutatud antud loogikaühendused FBD keeles.

NING-VÕI-tehte tulemuseks on signaal 1, kui vähemalt üks NING-lüli omab signaali 1. VÕI-NING tehte tulemuseks on signaal 1, kui mõlema VÕI-lüli tulemuseks on signaal 1.

Eitus

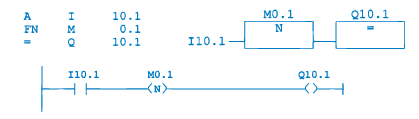

Binaarloogikas kasutatakse eitustehet sisendsignaali (operandi või muutuja) väärtuse inverteerimiseks ja edastamiseks lüli väljundisse. Eitustehte väljundsignaal on 1, kui sisendsignaal on 0 ja vastupidi. Joonisel 4.4 on kujutatud binaarloogika eitus LAD, FBD ja STL keeles.

Eitust saab kasutada ka NING- ja VÕI-lüliga seotud väljundlüli juures (joonis 4.5). Eitusega NING-lüli kutsutakse EI-NING-lüliks (NAND) ja VÕI-lüli EI-VÕI-lüliks (NOR) [6].

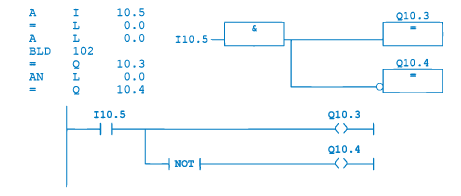

Loogikalüli operatsiooni (tehte) tulemuseks saadud väljundi (signaali) väärtust võib binaarloogika EI tehte abil ka inverteerida. Joonisel 4.6 inverteeritakse NING-lüli ja VÕI-lüli väljundi ja saadud tulemus antakse lisaväljundisse Q 10.4.

VÄLISTAV-VÕI-lüli

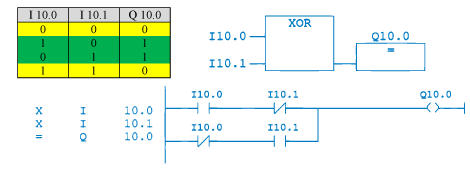

Binaarloogika VÄLISTAV-VÕI-lüli (VVÕI) väljundsignaaliks on 1, kui selle lüli kahe sisendi signaalid on erineva väärtusega. Kui ühe sisendi signaal on 1 ja teise oma on 0 siis VVÕI-tehte tulemuseks on signaal 1. Joonisel 4.7 on kujutatud binaarloogika VVÕI-lüli LAD, STL ja FBD keeles.

VVÕI-lüli võib omada rohkem kui kaht sisendit, sel juhul on VVÕI-lüli tulemuseks signaal 1, kui signaali 1 omavate sisendite arv on paaritu.

VVÕI-lüli saab kasutada koos NING- ja VÕI-lüliga.

SR- ja RS-trigerid

SR- ja RS-trigereid kasutatakse lüli sisendisse saabuva lühiajalise signaali oleku (eluea) pikendamiseks. Sisendsignaali väärtus salvestatakse lülis. Trigerid teostavad mälufunktsioone.

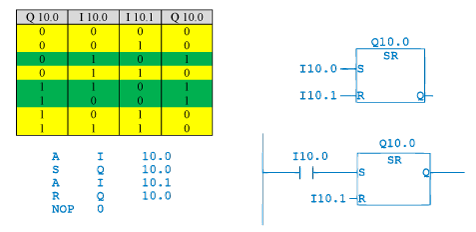

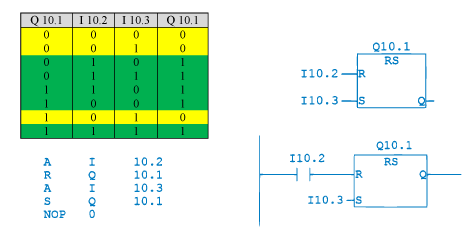

Joonistel 4.8 ja 4.9 on näidatud SR- (ülimusliku väljalülitamisega) ja RS- (ülimusliku sisselülitamisega) trigerid.

SR-trigeri väljundisse Q antakse signaal 1 kui trigeri sisendisse S (set) saabub signaal 1 ja sisendis R (reset) on signaal 0. See olek jääb kestma kuni trigeri väljalülitamiseni. Sisendi S signaali väärtuse muutus ei mõjuta väljundit Q, kui selle signaal on 1. Signaali 1 saabumisel sisendisse R muutub trigeri väljundi Q signaal 0 sõltumata sellest, milline on signaali väärtus sisendis S. Sisend R on ülimuslik. Seetõttu kutsutakse SR-trigerit ülimusliku väljalülitamisega trigeriks.

RS-trigeri väljundile Q antakse signaal 0, kui sisendis R on signaal 1 ja sisendis S on signaal 0. Trigeri olek jääb kestma kuni selle toite väljalülitamiseni. Väljundi Q signaal muutub 1 kui sisendisse S saabub signaal 1 sõltumata sellest, milline on sisendi R signaal. Seetõttu kutsutakse seda ülimusliku sisselülitamisega trigeriks. Signaali väärtuse muutus sisendis S ei mõjuta väljundit Q, kui selle signaal on juba 1 ning sisendis R on signaal 0.

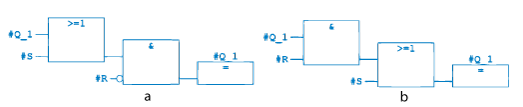

NING- ja VÕI-lülidest saab koostada SR- ja RS-trigereid (joonis 4.10).

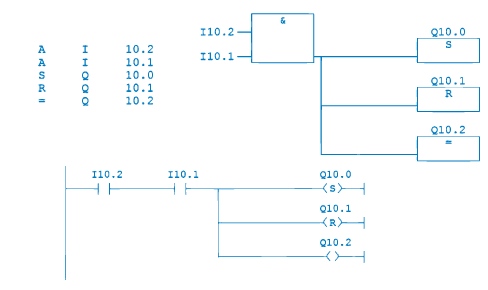

Operandi/muutuja väärtuse muutusi (ümberlülitusi) saab teha kasutajaprogrammi erinevates osades kasutades SET (S) ja RESET (R) funktsioone [6]. Nende funktsioonide kasutamne RS- ja SR-trigeris võimaldab teha eraldi sisse- ja väljalülitamise operatsioone. Puuduseks on ülevaate kaotamine programmis selle üle, mis tingimustel toimus mingi väljundi väärtuse muutus (trigeri lülitus). Samas saab üht sisendtingimust (signaali üht väärtust) kasutada rohkem kui ühe trigeri väljundi juhtimiseks (joonis 4.11).

Signaali väärtuse muutuse avastamine

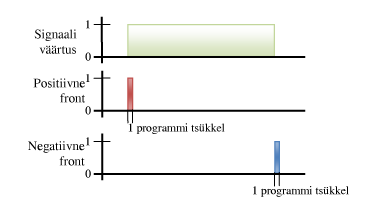

Füüsikalise signaali väärtuse muutumist mõõdetakse ja kasutatakse signaali oleku tuvastamiseks. Signaali väärtuse kasvamist (muutus 0 → 1) nimetatakse positiivseks frondiks ja signaali väärtuse vähenemist (muutus 1 → 0) negatiivseks frondiks [6]. Signaali väärtuse muutust kirjeldab lühike impulss väärtusega 1. Selle impulsi kestus on võrdne programmi 1 tsükli kestusega (joonis 4.12).

Signaali väärtuse muutuse (frondi) avastamiseks on PLCs olemas standardfunktsioon. Programmis tuleb kasutada eraldi operandi (muutujat), kuhu salvestatakse uuritava signaali olek programmi eelmises tsüklis. Signaali muutuse saab avastada ka NING-lüli ja SR- ja RS-trigeritega.

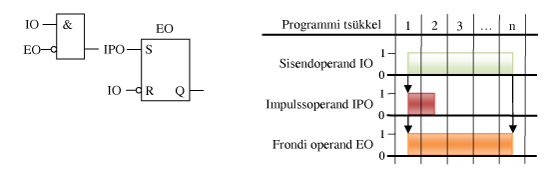

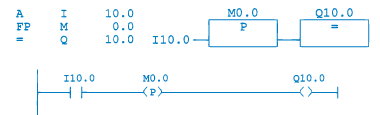

Tõusva (ehk positiivse) frondi funktsioon avastab sisendoperandi IO muutuse 0 → 1 (joonis 4.13). Sisendoperandi IO signaali hetkväärtust RLOs võrreldakse tema programmi eelmises tsüklis olnud signaali (frondi operand EO) väärtusega. Kui programmi eelmises tsüklis oli sisendoperandi IO signaal 0 ja nüüd on see 1, siis jääb RLO väärtuseks 1 ning impulsioperandi IPO signaal muutub "1" ainult antud programmi tsükli jaoks. Teiste juhtumite puhul on RLO ja impulssoperandi IPO signaalid 0. Frondi operandi EO salvestatakse programmi antud tsükli RLO olek, et seda võrrelda programmi järgmisel tsüklil sisendoperandiga IO [6].

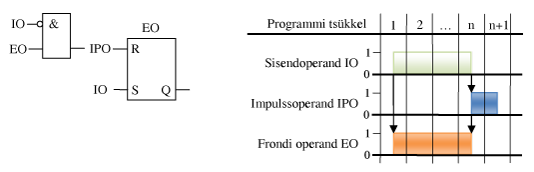

Langeva frondi funktsioon avastab sisendoperandi IO signaali oleku muutuse 1 → 0 (joonis 4.15). Sisendoperandi IO antud hetke signaali olekut RLOs võrreldakse tema (frondi operand EO) programmi eelmises tsüklis olnud signaaliga. Kui programmi eelmises tsüklis oli sisendoperandi IO signaal 1 ja nüüd on see 0, siis saab RLO väärtuseks 1 ning impulsioperandi IPO signaal muutub "1" ainult antud programmi tsükli jaoks. Teiste juhtumite puhul on RLO ja impulssoperandi IPO signaalid "0". Frondi operandi EO salvestatakse programmi antud tsükli RLO olek, et seda võrrelda programmi järgmisel tsüklil sisendoperandiga IO [6].

Standard IEC 61131 pakub käske R_TRIG (tõusev front) ja F_TRIG (langev front) signaali oleku muutuse avastamiseks.

Loogikatehted

Kaks muutuva väärtusega operandi (muutujat) või üks operand (muutuja) ja konstant ühendatakse omavahel loogikatehte abil. Standart IEC 61131 kasutab loogikatehete jaoks lihtsaid binaarloogika funktsioone. Need on AND, OR, XOR ja NOT.

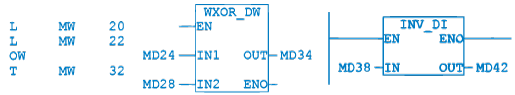

STEP 7 loogikatehted tehakse sõnadega, seejuures võrreldakse digitaalsete operandide paari teineteisega bitt biti haaval. Loogikatehetes kasutatavad operandid või konstandid peavad olema andmetüübilt sõna (WORD - 16 bitti) või topeltsõna (DWORD - 32 bitti). Tabelis 4.1 on esitatud STEP 7 loogikatehted LAD, FBD ja STL keeltes.

| Tehte nimetus | Sõna | Topeltsõna | Kommentaar | ||

|---|---|---|---|---|---|

| STL | FBD/LAD | STL | FBD/LAD | ||

| AND | AW | WAND_W | AD | WAND_DW | Loogiline NING tehe |

| OR | OW | WOR_W | OD | WOR_DW | Loogiline VÕI tehe |

| XOR | XOW | WXOR_W | XOD | WXOR_DW | Loogiline VVÕI tehe |

| NOT | INVI | INV_I | INVD | INV_DI | Eitus |

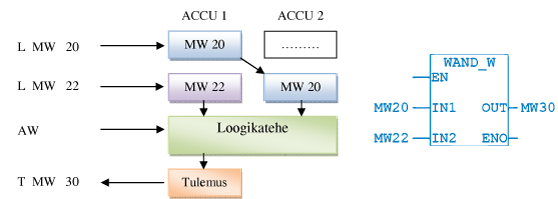

STEP 7 kasutab loogikatehetes protsessori registreid ACCU 1 ja ACCU 2 (joonis 4.17). Need on spetsiaalsed CPU registrid, mida kasutatakse lähteandmete puhverdamiseks loogikatehete teostamise eel (vaata lisaks peatükki 5.1). Esimese operandi (IN 1) väärtus laetakse ACCU 1-le. Teise operandi (IN 2) väärtuse laadimise eel kantakse kõigepealt ACCU 1 sisu edasi ACCU 2-le ja siis teise operandi (IN 2) väärtus ACCU 1- le. Edasi seotakse ACCU 2 (operand 1) ja ACCU 1 (operand 2) sisud omavahel vastavalt teostatava loogikatehte reeglile. Loogikatehte teostamise tulemusena saadud väärtus salvestatakse ACCU 1-le, kust see antakse edasi väljundoperandile (OUT) [6].

Binaarloogika NING-tehte tulemuseks saadud (topelt)sõna mingi bitt on 1, kui sisendoperandide vastavatel kohtadel olevate bittide väärtused on 1 (tabel 4.3). Binaarloogika NING-tehtega saab varjata/peita mittevajalikke või mitteolulisi bitte (nende väärtusi) operandis/muutujas. Selleks kasutatakse maski, mille abil vajalikud või olulises kohas olevad bitid saavad signaali 1 ja teised (varjatavad) signaali 0. Maskiks võib olla muutuja või konstant. Maskeeritav operand ja mask liidetakse binaarloogika NING-tehte abil kokku, kus mittevajalike bittide väärtused varjatakse (signaal muutub 0) ja oluliste bittide väärtused ei muutu. Tabelis 4.3 maskeeritakse sisendoperandi IN 1 bitid 2 ja 3 ning sisendoperandi IN 2 kasutatakse maskina.

Binaarloogika VÕI-tehte (topelt)sõna tulemuse mingi bitt on 1 kui sellele vastavate sisendoperandide bittidest vähemalt üks omab väärtust 1 (tabel 4.3). Antud loogikatehet kasutatakse bitimustri täiendamiseks. Binaarloogika VÕI-tehte abil lisatakse tulemuseks saadava kahendarvu ühte või mitmesse kohta signaal 1. Tabelis 4.3 oleva operandi IN 1 bittide 2 ja 3 signaalid peaksid olema 1. Selleks täiendatakse VÕI loogikatehtes bitimustrit lisades signaalid 1 operandi IN2 bittidesse 2 ja 3.

Binaarloogika VVÕI-tehte tulemuseks saadud (topelt)sõna bitt on 1 kui sellele vastavate sisendoperandide bittidest omab ainult üks bitt väärtust 1 (tabel 4.3). Antud loogikatehe võimaldab operandi bitimustris tuvastada signaali muutust ühes või mitmes biti kohas. Selleks liidetakse VVÕI-tehte abil kokku operandi vana ja uus bitimuster. Igas kohas, kus toimub signaali muutus 0 → 1 või 1 → 0, väljastab VVÕI-tehe signaali 1. Tabelist 4.3 on näha, et signaali muutus on toimunud bitis 1 (1 → 0) ja bitis 2 (0 → 1). Sisendoperand IN 1 omab vana bitimustrit ja sisendoperand IN 2 uut bitimustrit. Kui on vaja tuvastada signaali muutust 0 → 1, siis tuleb peale VVÕI-tehet teostata uue bitimustriga NING-tehe (tabel 4.2). Signaali muutuse 1 → 0 avastamiseks tuleb pärast VVÕI-tehet teostada vana bitimustriga NING-tehe (tabel 4.2).

| Signaali muutuse tuvastamine | Käsk | Näide | Kommentaar |

|---|---|---|---|

| Vaja tuvastada ainult signaali muutusi 0 → 1 | L MW 20 L EW 10 XOW L EW 10 UW |

…. 1010 …. 1100 …. 0110 …. 1100 …. 0100 |

Sõna vana biti mustriga Sõna uue biti mustriga ACCU 1 on muudetud biti muster Sõna uue biti mustriga ACCU 1 on lõpptulemus |

| Vaja tuvastada ainult signaali muutusi 1 → 0 | L MW 20 L EW 10 XOW L MW 20 UW |

…. 1010 …. 1100 …. 0110 …. 1010 …. 0010 |

Sõna vana biti mustriga Sõna uue biti mustriga ACCU 1 on muudetud biti muster Sõna vana biti mustriga ACCU 1 on lõpptulemus |

Binaarloogika EI-tehte tulemuseks on inverteeritud väärtusega sisendoperand. Loe selle kohta peatükist Matemaatilised ja teisendusfunktsioonid → Teisendusfunktsioonid → Teisendamine väärtuse täiendamisega.

Joonisel 4.18 on esitatud STEP 7 loogikatehte näiteid. STL keeles on esitatud binaarloogika VÕI-tehe sõna tüüpi muutujatega, FBD keeles VVÕI-tehe topeltsõna tüüpi muutujatega ning LAD keeles EI-tehe topeltsõna tüüpi muutujatega.

| Funktsioon | NING | VÕI | VVÕI | EI |

|---|---|---|---|---|

| Näide | IN 1: …. 1010 IN 2: …. 1100 OUT: …. 1000 |

IN 1: …. 1010 IN 2: …. 1100 OUT: …. 1110 |

IN 1: …. 1010 IN 2: …. 1100 OUT: …. 0110 |

IN 1: …. 1010 OUT: …. 0101 |